计算机组织与设计的软硬件接口 构建高效协同的桥梁

计算机系统是一个高度复杂的整体,其卓越的性能和功能并非仅仅源于强大的硬件或精妙的软件,而在于两者之间高效、无缝的协同工作。这个协同工作的关键,正是由“计算机组织与设计”这一学科所定义和实现的“软硬件接口”。它如同连接大脑与肢体的神经系统,是命令与执行、抽象与物理之间的核心桥梁。

软硬件接口的核心:指令集架构

软硬件接口最核心、最根本的体现是指令集架构。ISA是硬件提供给软件的一套抽象规范,定义了软件(特别是编译器和操作系统)能够看到和使用的处理器基本功能,包括:支持的指令类型(如算术运算、数据移动、控制转移)、指令的格式、寄存器组织、内存寻址模式以及异常和中断的处理机制等。

ISA是软硬件之间的“契约”。硬件设计者必须严格按照ISA规范来构建处理器,确保每一条指令都能被正确执行;而软件开发者(尤其是系统软件开发者)则基于这份“契约”来编写程序,他们无需关心晶体管如何开关,只需知道执行某条指令会得到确定的结果。经典的x86、ARM、RISC-V等都是不同的ISA,它们定义了不同的软硬件交互规则。

接口层次:从应用程序到晶体管

软硬件接口并非单一层面,而是一个多层次的分级体系:

- 应用程序接口:这是最高层的接口,如操作系统提供的系统调用、运行时库函数等。应用程序通过API请求服务,这些请求最终会穿透各层,触发底层的硬件操作。

- 操作系统与硬件接口:操作系统内核直接管理硬件资源。它通过设备驱动程序与特定的硬件控制器(如磁盘控制器、网卡控制器)通信,驱动程序了解硬件的具体寄存器细节和操作时序,将OS的通用请求翻译成硬件能理解的命令。

- 指令集架构层:如前所述,这是核心抽象层。机器语言程序(二进制代码)就是一系列ISA指令的集合。

- 微体系结构层:这是硬件对ISA的具体实现。相同的ISA(如ARMv8)可以由多种不同的微架构实现(如苹果的M系列芯片与高通的骁龙芯片),它们在流水线深度、缓存层次、乱序执行能力等方面可能大相径庭,但只要遵循ISA规范,就能运行相同的软件。微架构是软件“看不见”的部分,但它直接决定了性能、功耗和成本。

- 逻辑与物理层:最底层是门电路、晶体管和物理连接。微架构的设计最终在这里用硬件描述语言表达,并制成芯片。

接口设计的关键权衡与趋势

计算机组织与设计在定义软硬件接口时,始终在进行一系列关键的权衡:

- 性能 vs. 成本与复杂性:复杂的指令集可能提高代码密度,但硬件实现复杂;精简指令集硬件设计简单,但可能需要更多指令完成相同任务。

- 通用性 vs. 效率:通用处理器接口灵活,但针对特定领域(如AI、图形处理)可能效率不高。因此,现代系统广泛采用加速器(如GPU、TPU、NPU),它们通过特定的接口(如CUDA、OpenCL)与主处理器协同,形成异构计算架构。

- 抽象 vs. 控制:高级接口易于编程,但可能隐藏了硬件细节,不利于极致优化。因此,高性能计算、嵌入式系统等领域有时需要“接近硬件”的编程。

当前软硬件接口设计的主要趋势包括:

- 领域专用架构与接口:为人工智能、自动驾驶、生物信息等特定领域设计专用的计算单元和对应的编程模型/接口,以换取数量级的能效提升。

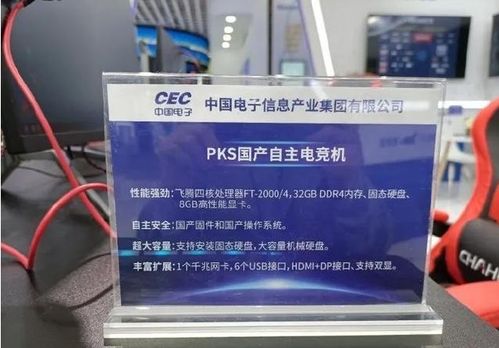

- 开放标准ISA的兴起:以RISC-V为代表的开放指令集架构,允许任何人在其基础上自由设计硬件和软件,极大地降低了创新门槛,推动了软硬件接口的定制化发展。

- 软硬件协同设计:打破传统的“先定ISA,再设计硬件,最后开发软件”的线性流程,针对特定工作负载(如某个算法或应用),同时优化算法、编程模型、ISA和微架构,实现整体最优。

- 安全接口的强化:在硬件层面引入信任根、安全飞地及其对应的软件接口,为操作系统和应用程序提供底层的安全支持。

结论

计算机组织与设计的软硬件接口,是计算机科学中工程与艺术结合的典范。它不仅仅是一份技术规范,更是一种设计哲学,决定了计算系统的能力边界、进化路径和生态格局。一个优雅、高效、可持续演进的接口设计,能够解放软件开发者的创造力,同时激发硬件设计者的创新潜力。随着计算需求日益多样化和专业化,如何设计下一代软硬件接口,使其在性能、能效、灵活性、安全性和开放性之间取得最佳平衡,依然是推动整个信息产业向前发展的核心挑战与机遇。

如若转载,请注明出处:http://www.cdsfl8888.com/product/74.html

更新时间:2026-02-24 03:13:18